Bharan Giridhar awarded Rackham Predoctoral Fellowship for research in circuit techniques for adaptive, reliable, high-performance computing

Giridhar’s research has an emphasis on developing circuit techniques for adaptive and reliable, high-performance computing.

Enlarge

Enlarge

Bharan Giridhar, a graduate student in the Electrical Engineering program, received a Rackham Predoctoral Fellowship to support his research while he completes his dissertation entitled, Circuit Techniques for Adaptive and Reliable, High-Performance Computing. The Rackham Predoctoral Fellowship is awarded to outstanding doctoral candidates in the final stages of their program who are unusually creative, ambitious and risk-taking.

Bharan’s research area is Very Large Scale Integrated (VLSI) chip design, with an emphasis on developing circuit techniques for adaptive and reliable, high-performance computing. To put his research in context with general trends, he states that, “the advancement in chip fabrication technologies has resulted in smaller and faster transistors with improved power efficiency. However, the demand for more on-chip features has constantly pushed chip size and power consumption to higher limits.”

To accommodate this growing power density and need for thermal management, designers are searching for energy-efficient methods to improve computation speed that go beyond simply leveraging clock frequency enhancement to improve chip performance.

Bharan is investigating three primary architectural and circuit techniques to bridge the power density gap: 1) Execution datapath to directly improve computation speed; 2) On-chip signal synchronizers to provide reliable, high-speed communication between on-chip components; and 3) Memory design and management in high speed computation systems (such as supercomputers).

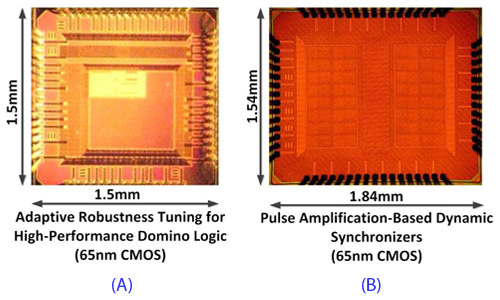

The following chip designs by Mr. Giridhar further the state-of-art in fast and reliable datapath design (A) and inter-clock domain on-chip communication (B).

Enlarge

Enlarge

Chip (A) proves a new design style, called Adaptive Robustness Tuning, (ART) that shrinks design margins and enables performance gains of ~71% over conventional domino logic. Margins are adaptively reduced until functionality errors are detected. These failures guide the tuning and are also corrected to guarantee forward progress in computation.

Chip (B) implements a new class of synchronizers for fast and reliable on-chip communication that improves MTBF over Jamb latches (used commonly for this purpose) by ~10ˆ6x at 2GHz in 65nm CMOS. Bharan is holding the fabricated chip in the photo above.

Bharan Giridhar is advised by Prof. David Blaauw.

MENU

MENU